新闻中心

【干货】MOS器件物理基础

摘要:

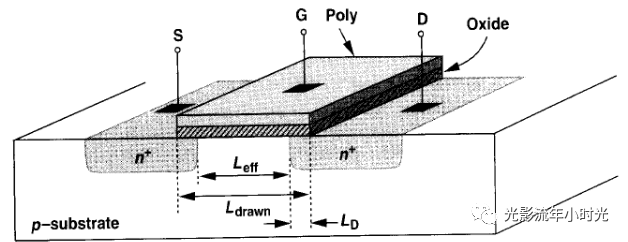

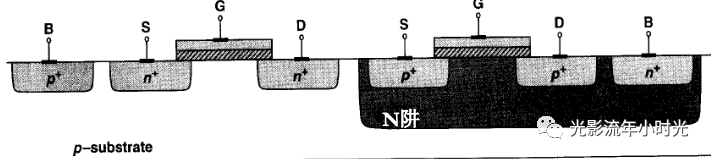

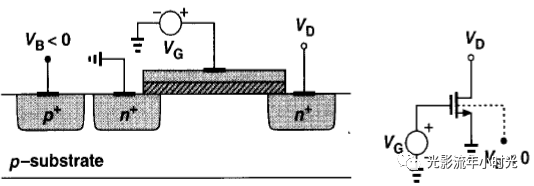

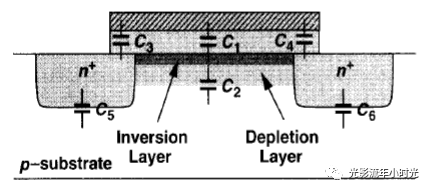

1、MOSFET的结构 (1)CMOS工艺截面图

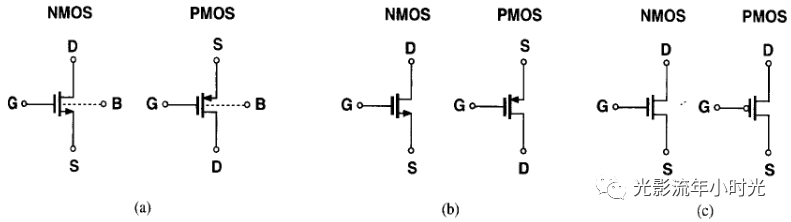

(1)CMOS工艺截面图 (2)MOS符号

(2)MOS符号 2.MOS的I/V特性

2.MOS的I/V特性

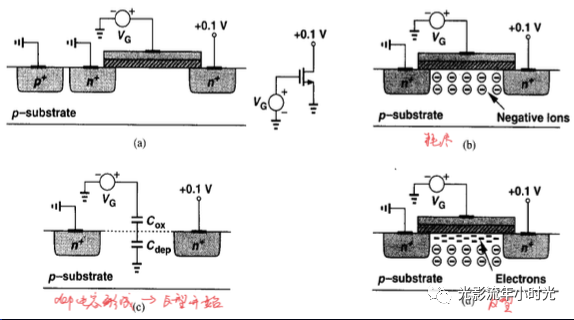

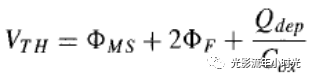

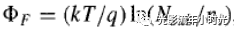

(1)阈值电压(VTH) NFET的VTH通常定义为界面的电子浓度等于P型衬底的多子浓度时的栅压。

NFET的VTH通常定义为界面的电子浓度等于P型衬底的多子浓度时的栅压。 ΦMS是多晶硅栅和硅衬底的功函数之差;

ΦMS是多晶硅栅和硅衬底的功函数之差;

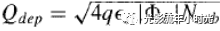

q是电子电荷,Nsub是衬底掺杂浓度,Qdep是耗尽区电荷,Cox是单位面积的栅氧化层电容,εsi表示硅介电常数。通过以上公式求得的阈值电压,通常为“本征(native)阈值” 典型值为-0.1V。在器件制造工艺中,通常通过向沟道区注入杂质来调整阈值电压,对于NMOS,通常调整到0.7V(依工艺不同而不同)。(2)MOS器件的I/V特性

q是电子电荷,Nsub是衬底掺杂浓度,Qdep是耗尽区电荷,Cox是单位面积的栅氧化层电容,εsi表示硅介电常数。通过以上公式求得的阈值电压,通常为“本征(native)阈值” 典型值为-0.1V。在器件制造工艺中,通常通过向沟道区注入杂质来调整阈值电压,对于NMOS,通常调整到0.7V(依工艺不同而不同)。(2)MOS器件的I/V特性

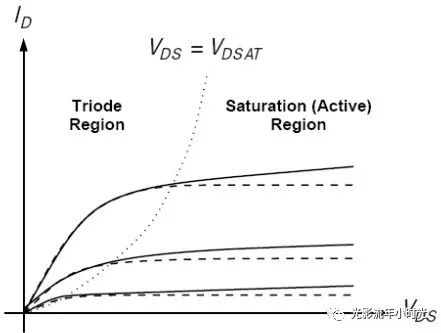

- 截止区(VGS<VTH)

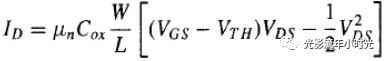

- 三极管区(线性区)(VDS<VGS-VTH)

- 饱和区(VDS>=VGS-VTH)

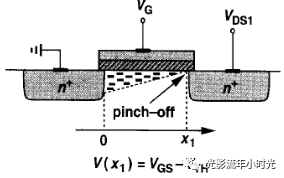

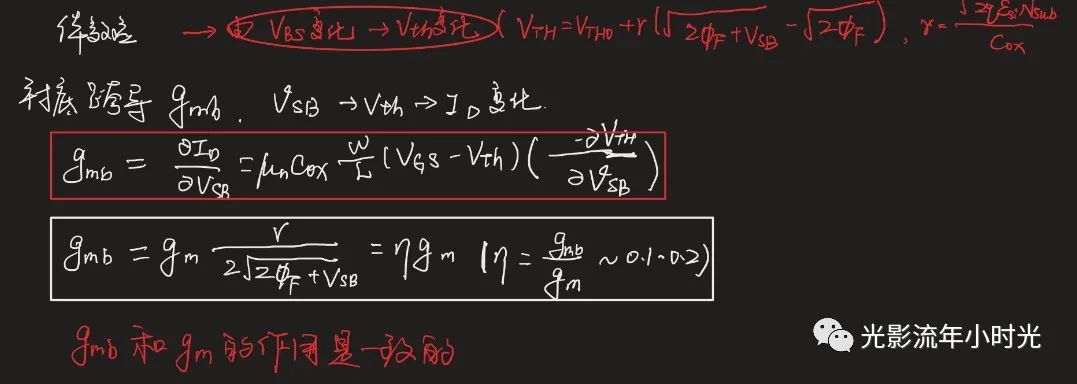

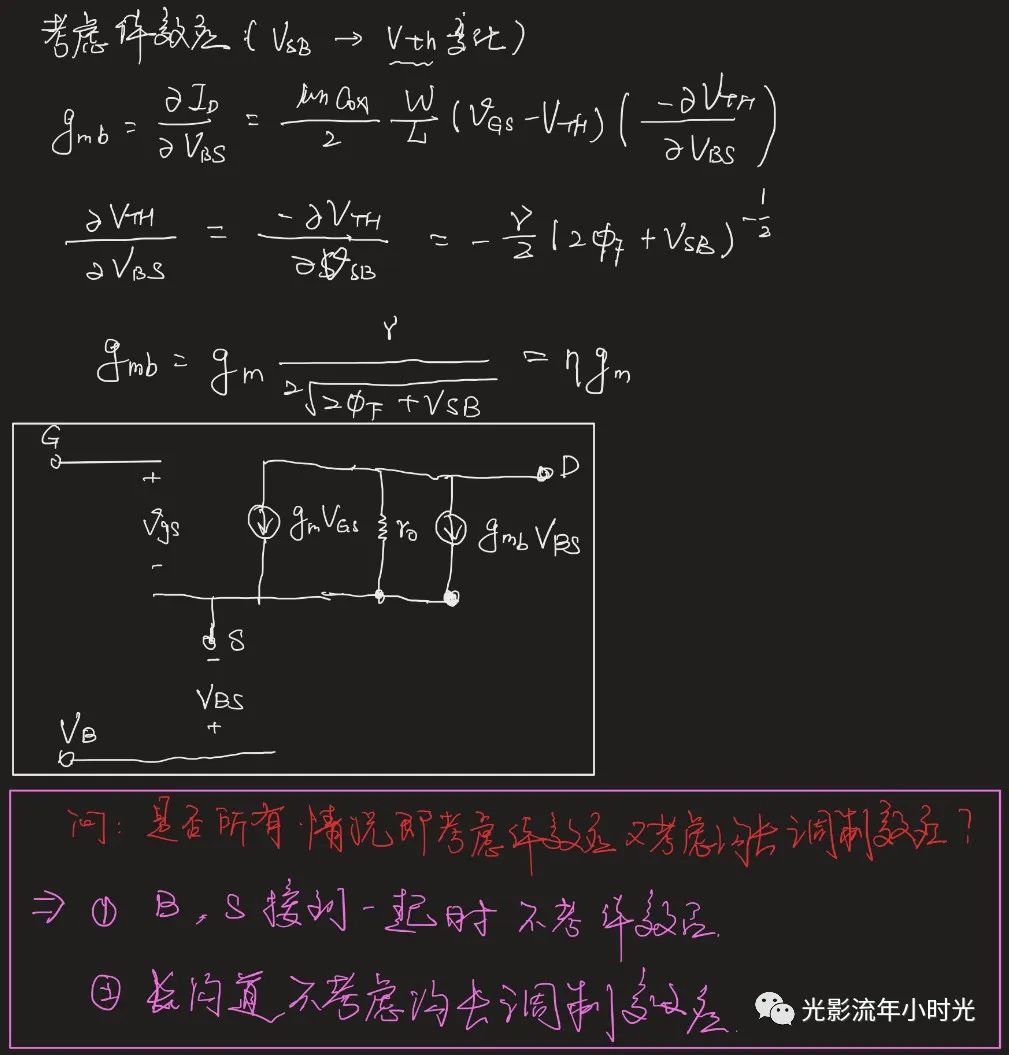

3.二级效应(1)体效应

3.二级效应(1)体效应

对于NMOS,当VB<VS时,随VB下降,在没反型前,耗尽区的电荷Qd增加,造成VTH增加,也称为“背栅效应”

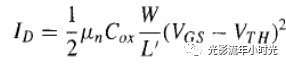

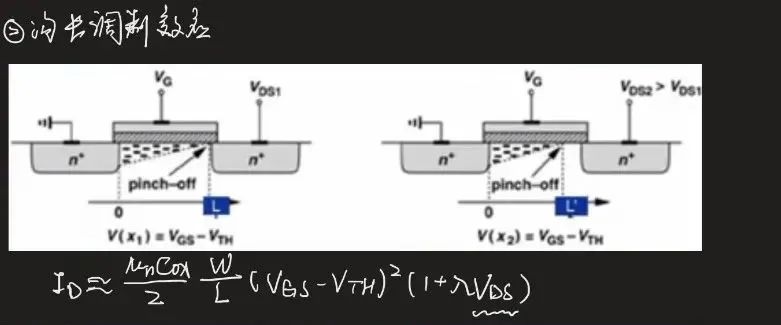

(2)沟长调制效应当沟道夹断后,当VDS增大时,沟道长度逐渐减小,即有效沟道长度L'是VDS的函数。

(2)沟长调制效应当沟道夹断后,当VDS增大时,沟道长度逐渐减小,即有效沟道长度L'是VDS的函数。

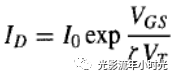

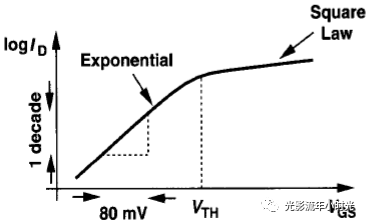

定义L'=L-△L,△L/L=λVDS (3)亚阈值导电性当VGS≈VTH时和略小于VTH,“弱”反型层依然存在,ID与VGS呈现指数关系。当VDS>200mV时。

(3)亚阈值导电性当VGS≈VTH时和略小于VTH,“弱”反型层依然存在,ID与VGS呈现指数关系。当VDS>200mV时。 这里ζ>1,VT =kT/q

这里ζ>1,VT =kT/q (4)电压限制

(4)电压限制

- 栅氧击穿:过高的VGS导致

- “穿通”效应:过高的VDS,漏极周围的耗尽层变宽,会到达源极周围,产生很大的漏电流。

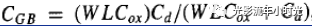

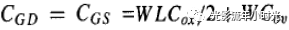

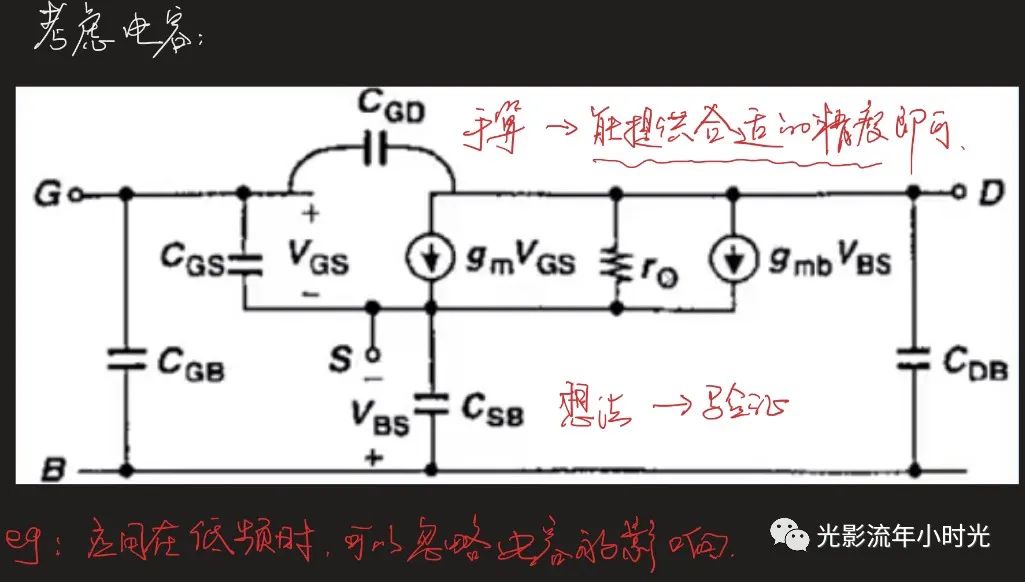

4.MOS器件电容

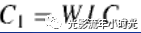

- 栅和沟道之间的氧化层电容:

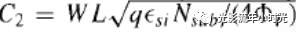

- 衬底和沟道之间的耗尽层电容:

- poly与 DS交叠而产生的电容C3,C4,每单位宽度交叠电容用Cov表示。

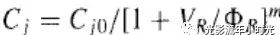

- DS与衬底之间的结电容C5,C6,结电容:

Cj0是在反向电压VR为0时的电容,φB是结的内建电势,m=0.3~0.4等效电容:

Cj0是在反向电压VR为0时的电容,φB是结的内建电势,m=0.3~0.4等效电容:

- 器件关断时,CGD=CGS=Cov*W

- CGB由氧化层电容和耗尽层电容串联得到

- 深三极管区时,VD≈VS,

- 饱和区CGD=Cov*W

在三极管区和饱和区,CGB通常可以被忽略。 5.MOS小信号模型

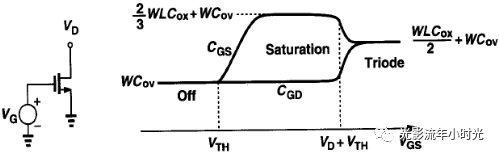

5.MOS小信号模型

- 大信号模型

Cgs等电容的电容值构成信号相对于偏置工作点而言比较大,会显著影响偏置工作点时用该模型。

- 小信号模型

信号相对于偏置工作点而言比较小,不会显著影响偏置工作点时用该模型简化计算。由gm,gmb,ro等构成低频小信号模型,高频时还需加上Cgs等寄生电容,寄生电阻(接触孔电阻,导电层电阻等)

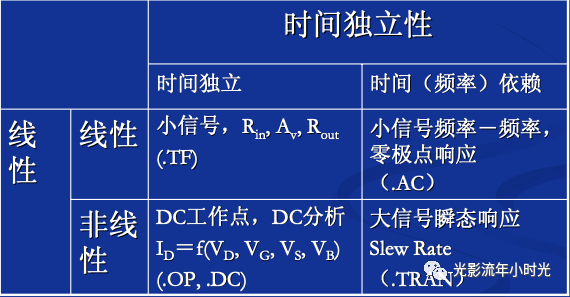

6.MOS SPICE模型

6.MOS SPICE模型

在电路仿真中,SPICE要求每个器件都有一个精确地模型。

(1)种类:第一代:MOS1,MOS2,MOS3;第二代:BSIM,HSPICE level=28,BSIM2;第三代:BSIM3,MOS model9,EKV(Enz-Krummenacher-Vittoz);Finfit工艺:一般为BSIM-CMG

目前工艺厂家最长提供的MOS SPICE模型为BSIM3V3

(2)仿真器:HSPICE;SPECTRE;PSPICE;ELDO等(3)基本的SPICE仿真

官方微信

官方公众号

电话:010-67882992 67892992 传真:010-67882992 邮箱:[email protected] QQ:55890894